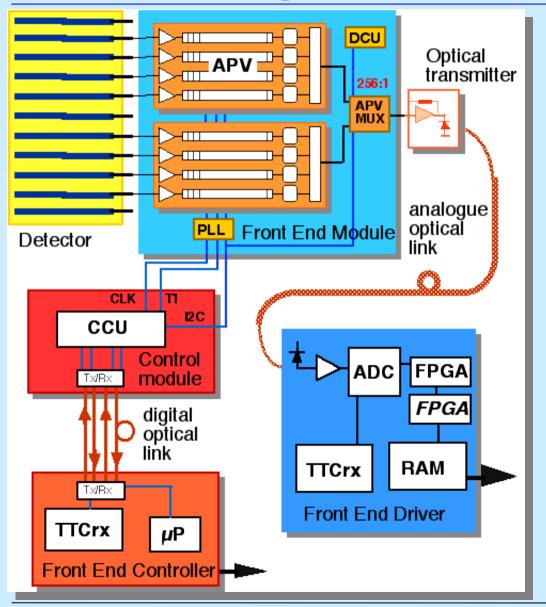

## CMS microstrip tracker readout

- Front end almost complete APV25 frozen final DCU, MUXPLL submitted 0.25µm contracts in place

- **Optical link** *very advanced state* ready to start procurement

- DAQ interface *PMC FED exists* final FED being designed

- Control system *well advanced* FEC & 0.25µm chip set exist

- System

1

under construction in CERN lab 25nsec beam May 2000

## **Optical link status**

- Project entering production phase

- Feasibility demonstrated with close to final components

- Robustness & radiation tolerance measured

- Market surveys for all elements in the chain

- Manufacturers of lasers and connectors short-listed

- Final calls for tender needed mid 2001

Final system and costs depend on tender actions NB non-trivial to manage these large tenders *interdependent components, booming electronic*

market, special requirements,

small volumes cf commercial demand

2

# Why analogue optical link PRR now?

• Optical link components well factorised from remainder of readout system but tightly linked in finalising system

Exhaustive scrutiny of component performance (& manufacturers)

final components (and costs) needed (ESR) but...

...can't procure pre-production components without completion of tenders some system elements (eg FED) can't be finished without final optical links final FED now essential for large scale acceptance tests from 2002

• Now need to make commitments

Commercial procurement on large scale (for HEP)

• This talk - snapshot of system

Main missing information

system tests with modules in realistic mechanical & electrical environment

• Glossary (offline) please see

http://pcvlsi5.cern.ch/CMSTControl/documents/GeneralDoc.htm

Readable system summary + references to considerable published information

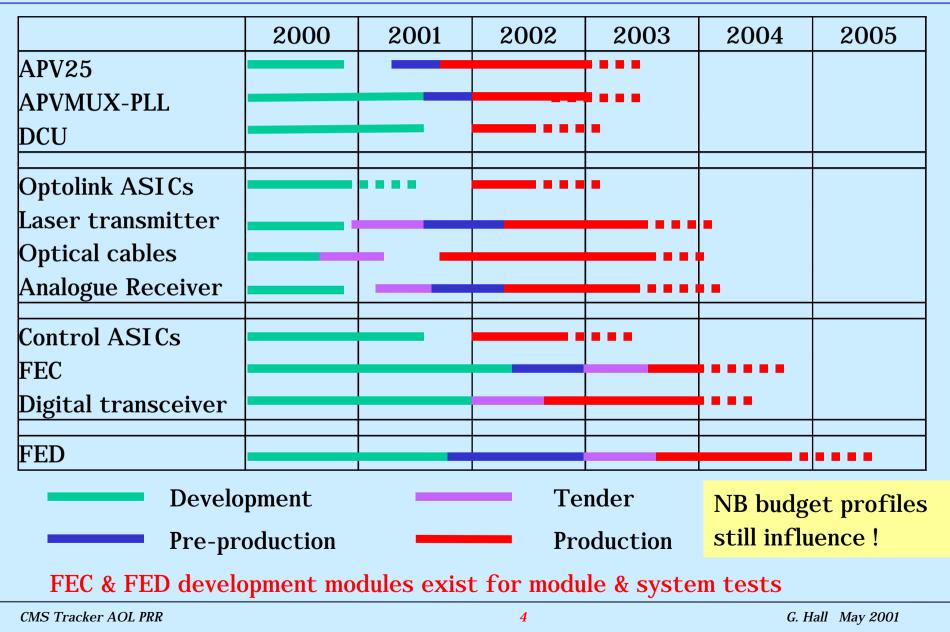

# Major components and schedule

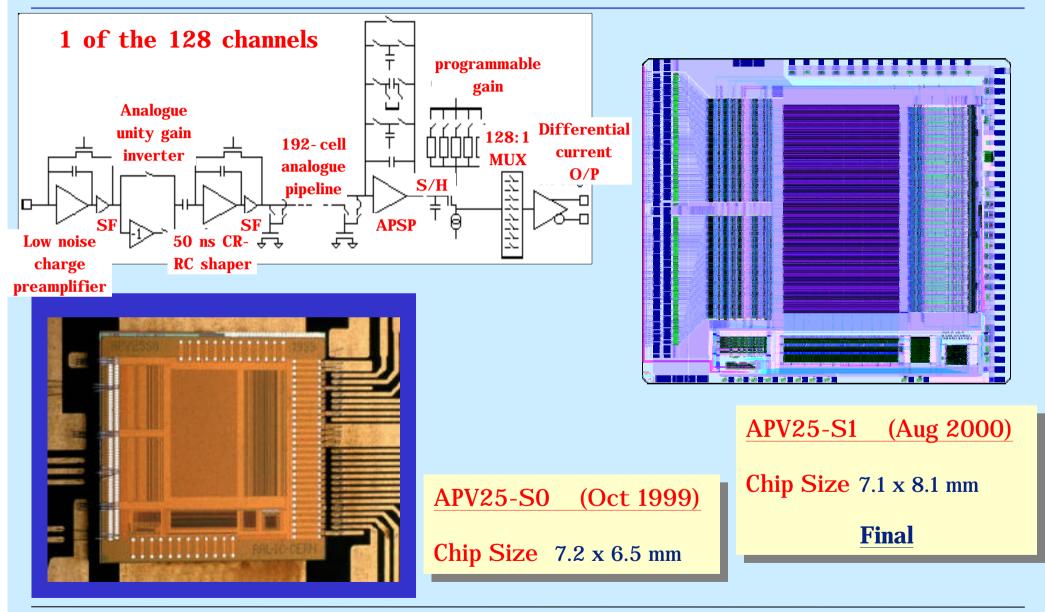

# **APV25 0.25μm CMOS**

CMS Tracker AOL PRR

# New features in 0.25µm APV

• Motive for late change of technology

Radiation hardness from standard reliable process & significant cost gains

• Strategy

only changes essential for new process *e.g. 2.5V power supply*

- + few system level enhancements e.g.

- Longer pipeline 192 [160]

- Deeper buffers 10 (x3) [6 (x3)]

- S/N improved 2000/0.36 PMOS @ 400μA [3000/1.4 PMOS @ 500μA]

- Switchable input polarity & differential output

| • | Reduced size         | 57mm <sup>2</sup> | [77mm <sup>2</sup> ] |

|---|----------------------|-------------------|----------------------|

| • | <b>Reduced power</b> | 2.3mW/channel     | [2.4 + MUX]          |

• All benefits realised... entire system based on single 0.25µm process

CMS Tracker AOL PRR

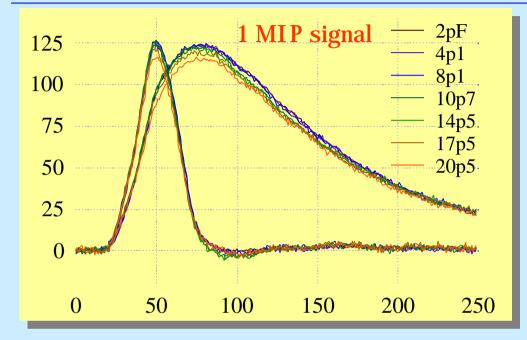

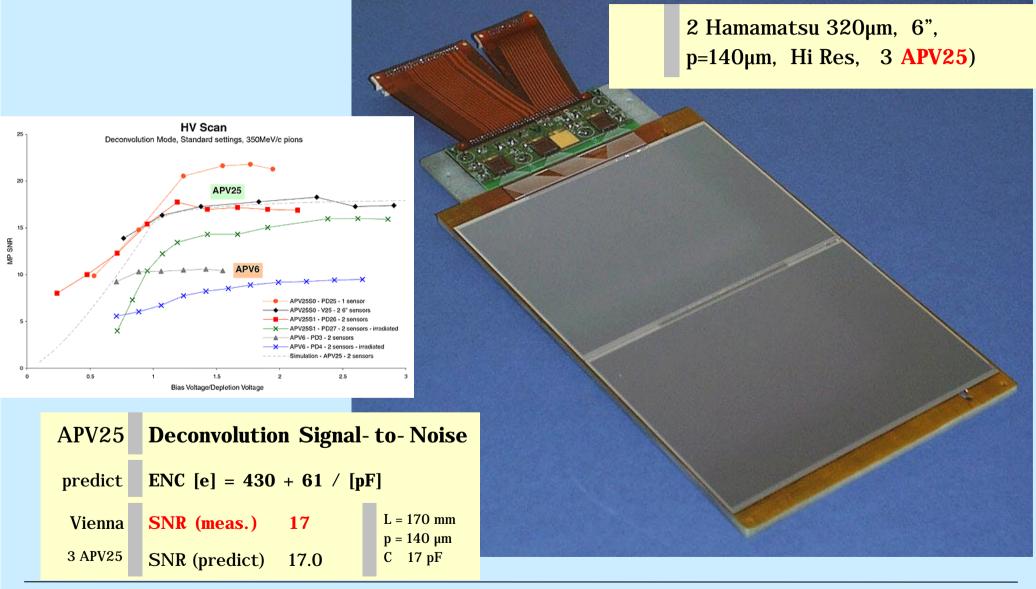

# Typical lab test results APV25-S1

- < 5 % non-linearity to 5 MIPs

- **Pipeline pedestals & gain uniformity** additional noise typical < 150e

- Significant speed & V<sub>supply</sub> margins

- Good noise uniformity

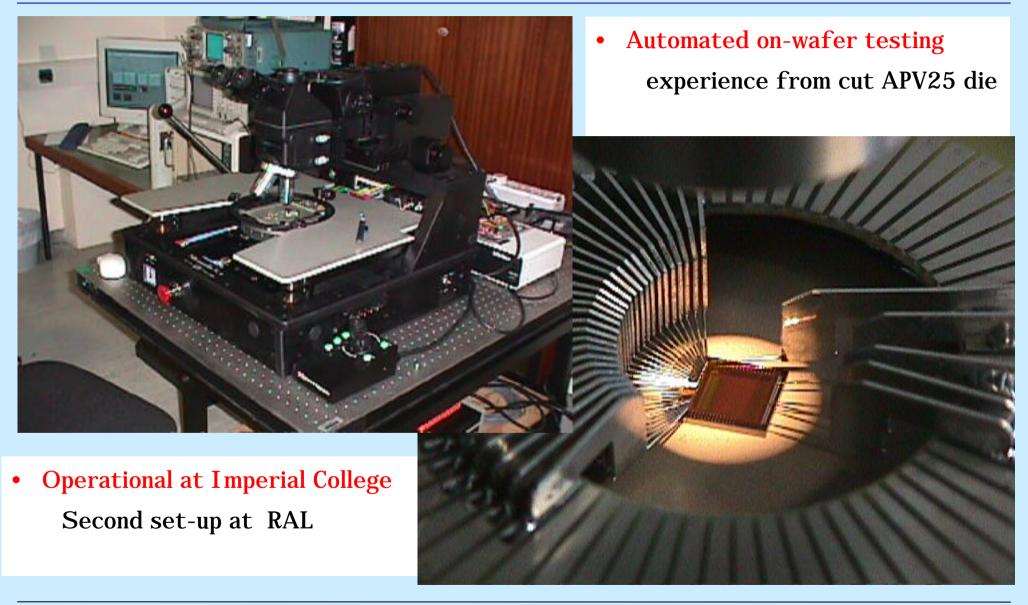

# **Chip testing**

# Chip testing summary

### • Digital functionality

• Power supply currents

### • Analogue tests

**Every channel**

Every pipeline location

only noise not measured on-wafer

### to be used in production

| _    |                                                                                      |

|------|--------------------------------------------------------------------------------------|

| Bas  | ic digital functionality                                                             |

|      | I2C functionality (read/write to all locations, test for stuck bits, response to all |

|      | possible chip addresses)                                                             |

|      | Check for correct address in digital header                                          |

|      | 0                                                                                    |

|      | Look for header error bit set after 1000 pseudo-random triggers                      |

| Pow  | er supply currents                                                                   |

|      | Verify VDD and VSS currents within acceptable range                                  |

|      |                                                                                      |

| Pipe | eline                                                                                |

|      | Measure pedestals for every pipeline cell for all channels, look for bad locations   |

|      | (high/low pedestals) and correct pipeline column address in header                   |

|      |                                                                                      |

| Cha  | nnel pedestals                                                                       |

|      | Verify analogue baseline can be adjusted and measure pedestals, look for high/lo     |

|      | channels. Do this in both peak and deconvolution modes.                              |

|      | chamics. Do this in both peak and acconvolution modes.                               |

| Cha  | nnel calibration                                                                     |

|      | Measure pulse shape for all channels in peak and deconvolution modes.                |

|      |                                                                                      |

|      | Look for bad channels (low pulse heights).                                           |

- Test time < 2mins/chip

- => 1 8inch wafer per probe station per day

- => Complete testing in ~1 year

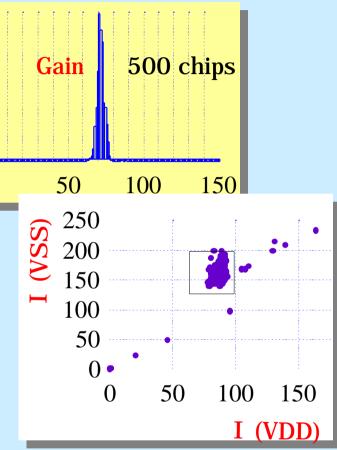

## **APV25** chip testing results

Consistent high quality from MPW and 10 wafer order APV25-S0 passed <u>all</u> tests: 84% (500 die) APV25-S1 cut wafer yield : 66% (~222 die)

Uniformity excellent

• 8 inch APV25-S1 wafer testing under way

3/9 wafers tested to date

refining final tests, criteria & software

Data base prepared

Do not expect problems to match module production schedule

draft QA document exists (for all chips)

# **APV25** wafer test results

|              | JLCS9NT  | JOCSEPT | JICS9RT | Total |        |       |          |                |      | 2      | 1      |        |       | 123   | EXEL 3 | 901.7<br>III8 | 1118 | 1119 | HIL I H    | ALL I             | 5      | J                   | Ι         | CS             | 59F                                                                                                            |

|--------------|----------|---------|---------|-------|--------|-------|----------|----------------|------|--------|--------|--------|-------|-------|--------|---------------|------|------|------------|-------------------|--------|---------------------|-----------|----------------|----------------------------------------------------------------------------------------------------------------|

|              |          |         |         | Fails |        |       |          |                | 1    | NIL 17 |        |        | ш.    | 111   | 1      | 118           |      |      | _          | 101 100<br>103 10 |        | RE I                |           |                |                                                                                                                |

|              |          |         |         |       |        |       | 2        | 8612 (<br>6012 | 4117 | 101    | 171.7  | EU 12  | 1 30  | 110   | 1111   | 117           | 107  | nu.  | нр         | 1111              | E7 1   | 87 20               |           |                |                                                                                                                |

| Digital      | 68       | 52      | 48      | 168   |        | 1     | 曲        | DES 1          | 015  | 163    | 125    | 01 18  | 96 JD | 1206  | 1234   | 1118          | 3116 | 1)1ł | 1815       | 1136 (            | 81.6 1 | 86 (B)              | 3         | ( 234          | 1                                                                                                              |

| <u> </u>     |          |         |         |       | 1      | ENT.  | ttt      | 6425           | 613  | 163    | 173    | 85 P   | 5 20  | 110   | 1111   | III.          | 3415 | лii  | 1K2        | mi ji             | n i    | R5 (22)             | 5 22      | - history      | The second s |

| Power        | 4        | 6       | 3       | 13    |        | 101   | 101      | 0.11           | 411  | 101    | 173    | EX B   | 23    | 221   | 111    | ш             | 3118 | 718  | 163        | 1711 1            | EI 1   | RI 20               | 1 23      |                | NIT:                                                                                                           |

|              |          |         |         | 1     | 1      |       | 113      | 613            | 613  | 83     | 1717   | EI 18  |       | in    | 1115   | 1111          | 1413 | 1115 | 183        | mi i              | 0      | 80 20               | 1 22      | 1 201          |                                                                                                                |

| ripeline     | 9        | 6       | 8       | 23    | tu     | 411   | th       | 2412           | e112 | 82     | 72     | 12 12  | 2 33  | 122   | 111    | 111           | 101  | 111  | 182        | mi                | 12     | 97 M                | 1 22      | 1 22.11        | 2112 11                                                                                                        |

|              |          |         |         |       |        | tii   | atri.    | 46             | en 1 | NII    | 120    | ti y   | a m   | 1 200 | 1211   | ,tti          | 1411 | щ    | IRI<br>IRI | ttu i             | 81.1   | RI III              | 2.1       | 211            | रेता अंध                                                                                                       |

| Channels     | 36       | 26      | 25      | 87    | 00 I.I | 1 110 | \$12     | 461            | £110 | 82     | 17.0   | 12 2   | 4 31  | 200   | 3130   | 111           | 1111 | 1910 | 183        | 1110 1            |        | 11 12               | 1 23      | 1000           | 201 30                                                                                                         |

| & calibr.    |          |         |         |       | U.     | 0 410 | 110      | \$109          | 0.0  | 18/7   | 1708   | 11 1   | 1 34  | 20    | 1709   | 187           | 1408 | 777  | 1939       | 100 1             | 10 1   | N9 30               | \$ 2.0    | 1 2319         | 2309 240                                                                                                       |

| <b>Fotal</b> | 117      | 90      | 84      | 291   |        | 8 628 | 118      | 6408           | 613  | 88     | 1798   | 12     | 19 28 | 128   | 1398   | 131           | 3408 | 379  | 148        | 1428 1            |        | X8. 20              | 1 7.8     | 1 238          | 238 340                                                                                                        |

| (adra)       |          |         |         | 8     | 100    | 1 20  | 1317     | 6827           | 07   | 101    | 99     | 80 10  | 1 3   | 1 201 | 100    | UT.           | 147  | yyr  | 1947       | 107 1             | 10     | 10                  | 1 28      | 1 2311         | ALL NALL                                                                                                       |

| (edge)       | (60)     | (49)    | (48)    | (157) |        | 215   | <u> </u> | 6496           | 6126 | 105    | 100    | 101 27 | 1 70  | 120   | 2254   | 2386          | 1456 | 7154 | 186        | 126 1             | 46 1   | NS 30               | 4 72      | 6 2206         | 226 226                                                                                                        |

| lield        | 70 %     | 77 %    | 79 %    | 75 %  | À      | 03    | 1315     | 6405           | 015  | 145    | 005    | 10 10  | 1 28  | 220   | 100    | 130           | 3455 | 100  | 185        | -                 |        | 305 200<br>11 Frank | 1,1,1,1,1 | and the second | 圞                                                                                                              |

|              | /0 /0    | ////0   | 13 /0   |       | 3      | 1     | 1364     | \$408          |      |        |        | 81 19  |       |       |        | 1314          | 1406 | 200  | 1938       | 1774              | a f    | Ke (=               | 1 25      | 1 234          | 1                                                                                                              |

|              |          |         |         |       |        |       |          | 107            | 810  | NIL I  | 2761   | -      |       | 2007  | 101    | 181           | 1408 | 2011 | 1803       | 100 1             | m      | N0 20               | 1         |                |                                                                                                                |

| • Cut        | wafer re | test    |         |       |        |       |          |                | 555  | 100    | iner 1 | . 6    |       |       | -111   | 181           | 100  | 1940 | 189        | 102 1             | 100    | ··· 🛗               | 1         |                |                                                                                                                |

wafer cut poor quality but still <2% good die failed and then you have

NAL TIME OVER

## 300 MeV/c beam test (Vienna)

CMS Tracker AOL PRR

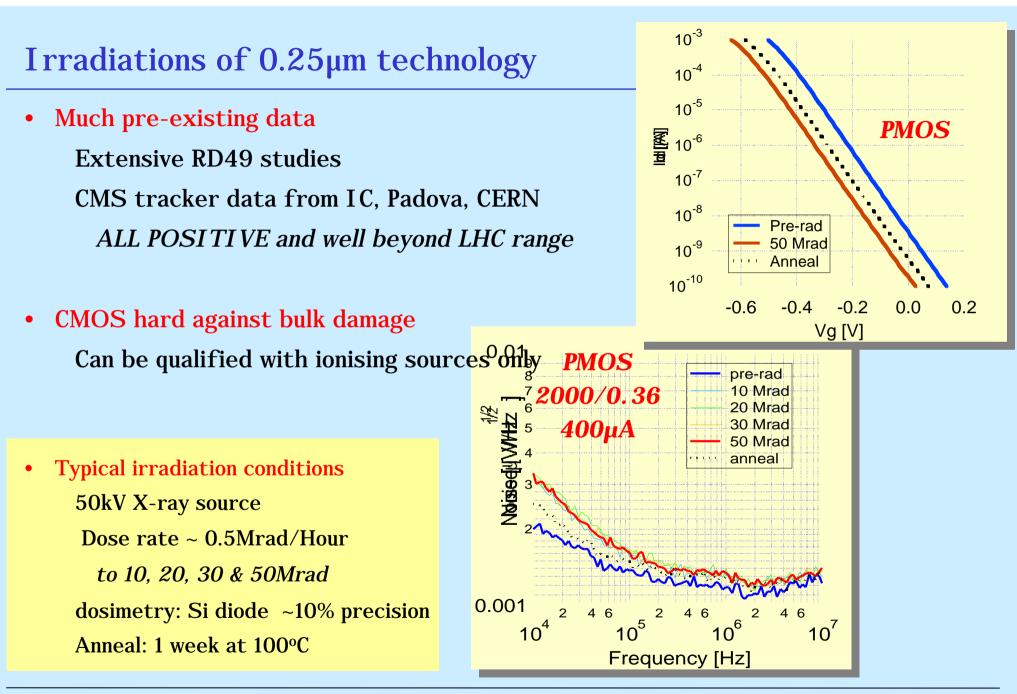

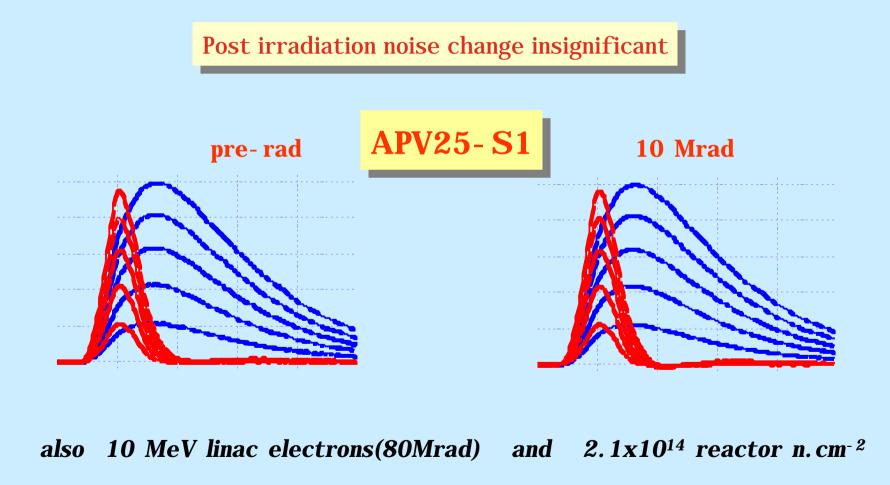

## APV25 irradiations (IC & Padova)

• IC x-ray source

Normal operational bias during irradiation

clocked & triggered

CMS Tracker AOL PRR

# Single Event Upset tests Heavy ions and pions

| Ion                                                  | Si       | Cl        | Ti        | Ni        | Br | Ι  |

|------------------------------------------------------|----------|-----------|-----------|-----------|----|----|

| LET<br>(MeV. cm <sup>2</sup><br>. mg <sup>-1</sup> ) | 9-<br>10 | 13-<br>16 | 20-<br>23 | 28-<br>32 | 39 | 62 |

|                                                      |          |           |           |           |    |    |

local highly ionising particle near sensitive circuit node can change state of logic elements

origin - knock-on silicon ions in chip

- 4 APV25s in three tests Feb 2000, July 2000, Dec 2000

- Measured circuit cross-sections include in CMS Simulations

- Conclusions <u>full system</u>

~150 SEU per hour

= 0.15% APV25s

verified in π beam Dec 2000

Technology very robust

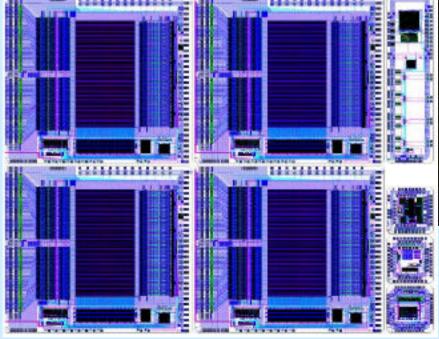

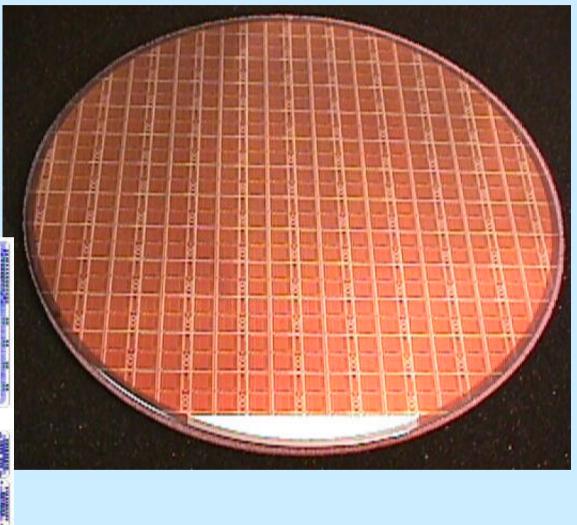

# **Production wafer layout**

- Overall size 200mm

- APV25 die 400

- APVMUX+PLL die 100

Reticle dimensions 18,420mm x 14,400mm

CMS Tracker AOL PRR

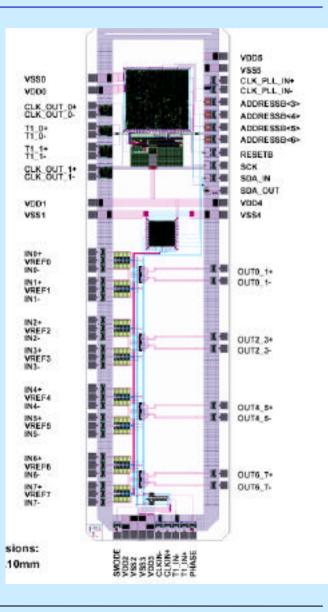

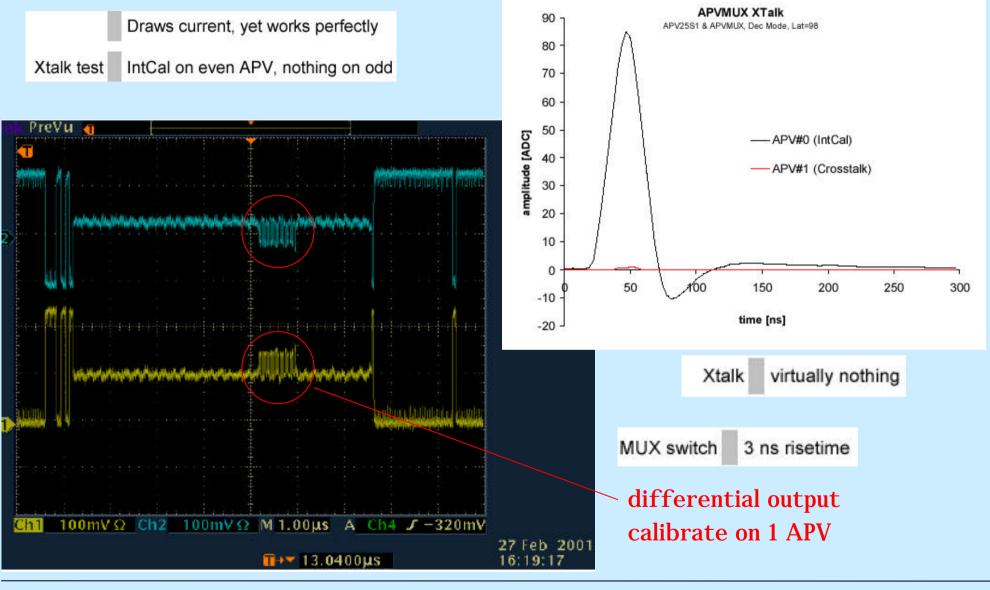

# Other FE chips (i) APVMUX-PLL

- to ease production, FE PLL + APVMUX as single chip electrically independent

- PLL guarantees good clock & T1 on module

*+ fine tuning of delay* individual version successfully tested

- APVMUX interleaves 4x2 APV 20MHz data streams

*=> transmission switch* die delivered August... problem on test extra power

- Resubmitted October MPW run (-> March 2001) single mask layer change to correct fault further minor fault - resubmit May 2001

- Main impact now on schedule need to finalise FE hybrid

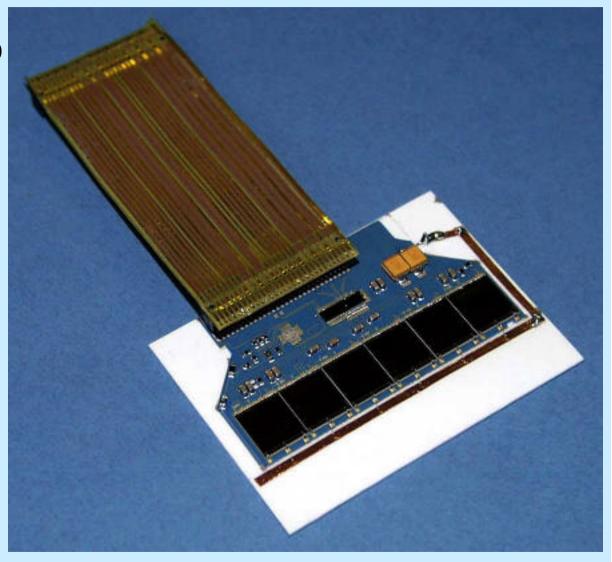

# FE hybrid (Strasbourg)

- Ceramic hybrid Choice of technology Oct 2000

- First TIB hybrid Nov 2000

CERN workshop manufacture

PLL-MUX problem complicates

operation

problem with 30m resistance

solved + ...

- ... robust at system level

- TOB hybrid delivered April 2001 to deliver system test

- Industrial production foreseen Market survey beginning

CMS Tracker AOL PRR

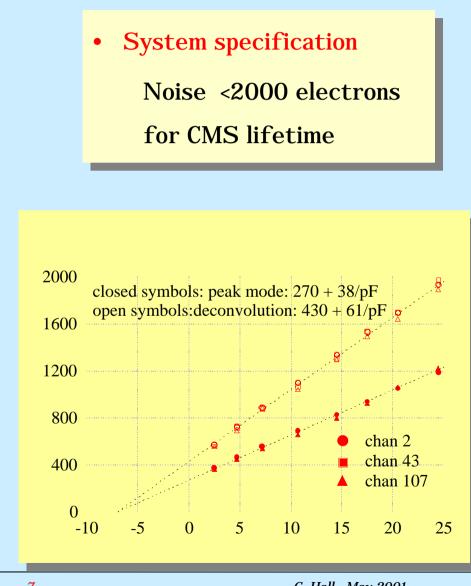

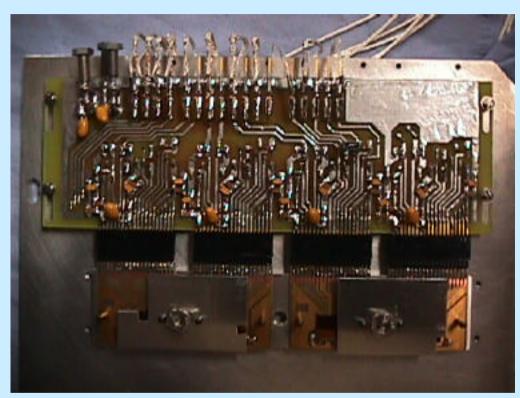

# Hybrid test in Vienna Feb 2001

• Readout system as used in beam and SEU tests

| System        | 6 APV25 + APVMUX $\rightarrow$ 3 analog channels         |       |     |       |  |  |  |

|---------------|----------------------------------------------------------|-------|-----|-------|--|--|--|

| IntCal        | 1 MIP level (ICAL=36)                                    |       |     |       |  |  |  |

|               | Typical IntCal Signal and Noise values                   |       |     |       |  |  |  |

|               | Noise [e] is calculated assuming 22500 e<br>from ICAL=36 |       |     |       |  |  |  |

| (no detector) |                                                          |       |     |       |  |  |  |

| Mod           | e Signal                                                 | Noise | SNR | Noise |  |  |  |

| Mode          | [ADC] | [ADC] | ONIX | [e] |

|---------------|-------|-------|------|-----|

| Peak          | 72    | 1.10  | 65.5 | 344 |

| Deconvolution | 83    | 1.58  | 52.5 | 428 |

Dec Noise ENC [e] = 400 + 60 / [pF] good agreement

# **APVMUX performance on hybrid**

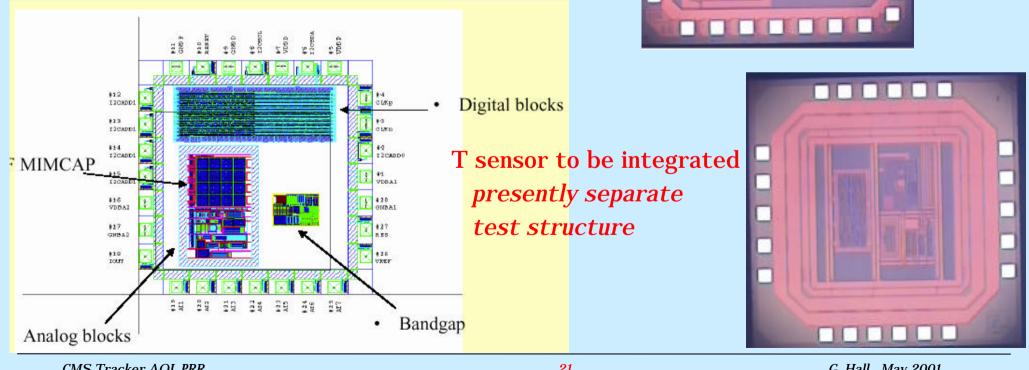

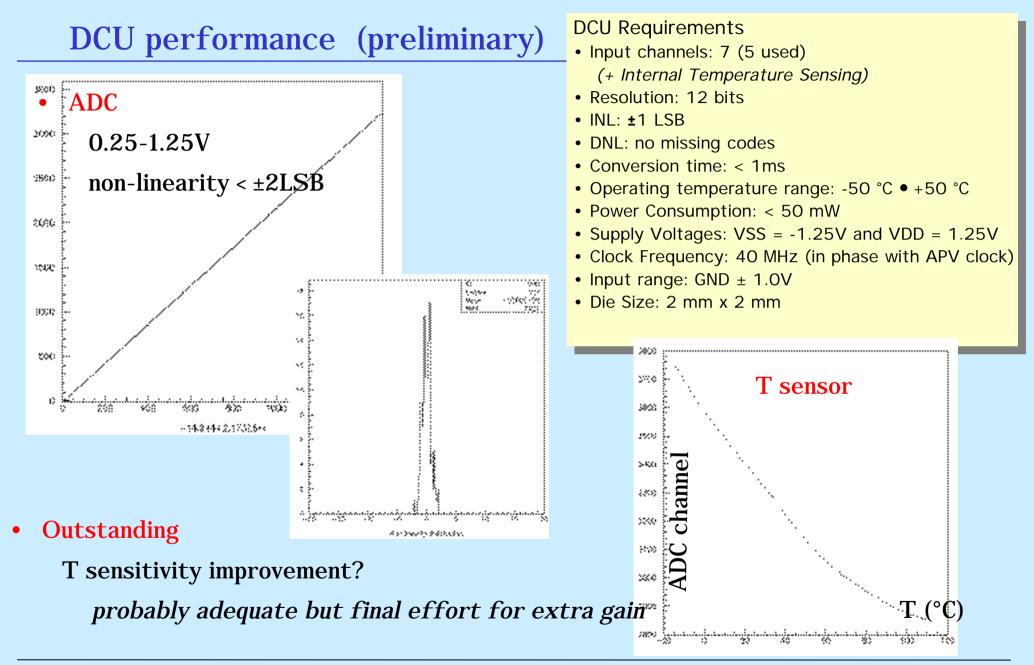

#### Other FE chips (ii) DCU

- Current, temperature and V<sub>supply</sub> monitoring Specifications & footprint frozen chip fabricated, first iteration problem second version meets requirements possible fine tuning

- Freeze summer 2001

CMS Tracker AOL PRR

## **Radiation qualification**

• stable process

verify wafers within manufacturer's specs, data base to record

• stable performance

electrical measurements of APV25 (& others) most statistics, detail, and prompt

• total dose irradiation

samples from 10% wafers

APV25 & test structure in <u>both</u> UK & Padova = 20% x-ray, <sup>60</sup>Co, 8MeV e available

- irradiations of other components evidence of hardness is cumulative

- other effects SEU, SEGR

much data now exists, cumulative

### NB all CMOS hard against bulk damage

NB hardness relies on intrinsic hardness of technology (oxide) enclosed geometry nMOS

NB no evidence of technology weakness 0.25µm statistics exceed most other processes

|                                    | ASIC    | Function        | Status in        | Number |

|------------------------------------|---------|-----------------|------------------|--------|

| Control system                     |         |                 | 0.25µm           |        |

|                                    | CCU25   | Master of       | Rad soft version | 4000   |

| • Non-critical path items - so far |         | control network | Submit 5/01      |        |

| • during 2001                      | LVDSMUX | Clock routing   | Working          | 4000   |

|                                    | LVDSBUF | Buffer          | Working          | 10000  |

| complete ASICs                     | RX40    | Digital optical | Complete         | 1000   |

| verify operational performance     |         | receiver        |                  |        |

| plan manufacture                   | LD      | Laser driver    | Prototyped       | 20000  |

| 1                                  |         |                 | Final 5/01       |        |

| assemble on common wafer           | PLL25   | Clock integrity | Complete         | 4000   |

| for cost reasons                   |         | & delay         |                  |        |

Remaining issues are essentially:

cost management

logistics

manufacture & packaging

test

assembly

## Schedule ASIC chips

• APV25-S1

10 wafers in hand ~2500 APV25 DCU & APVMUX-PLL ok for current tests

- Final APVMUX-PLL tested September 2001 May MPW run (=>August) Once proven, production masks frozen

- Further engineering run obligatory verify final masks

- Launch 50 wafer production July? cost \$120k verify large scale test procedures, data handling & storage

- Ancillary chips

common wafer early 2001

Sufficient for >200 modules + other tests

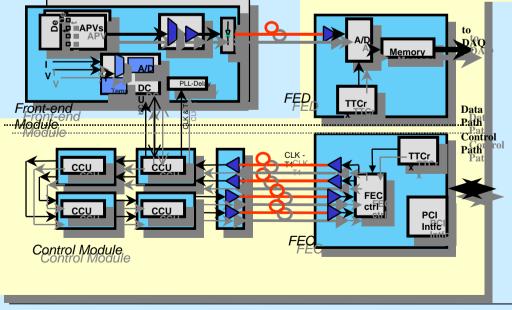

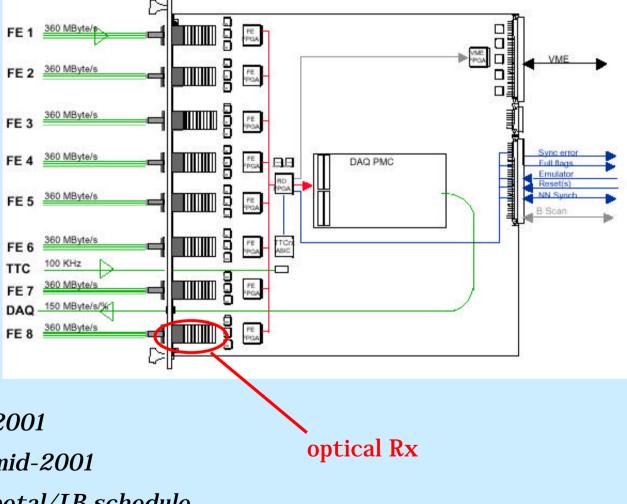

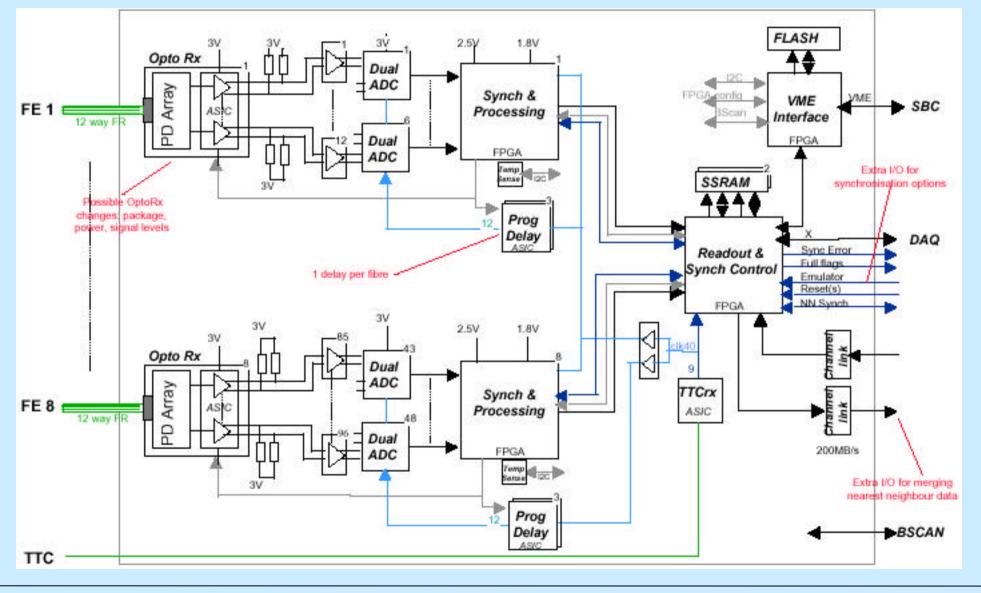

# Front End Driver - Tracker-DAQ interface

### • 8 channel PCI module in use

### ok for module testing

- Final FED 9U VME module 96 optical channels

- Schedule

design study to end 2000 User Requirements April 2001 pre-production prototype mid-2001 production match to rod/petal/IB schedule

# **FED functionality**

CMS Tracker AOL PRR

# **Power supply system** (Firenze + Torino)

• Specifications defined

• Challenging subject

Long cables No internal regulators Unbalanced I + & I - in APV Scope for noise in power delivery to module, clocks

• System test required

| July-Dec 2000  | Commissioning of DAQ system.                                                         |

|----------------|--------------------------------------------------------------------------------------|

|                | Cable selection and procurement.                                                     |

| Nov 2000:      | Delivery of cables.                                                                  |

|                | Test of cable electrical specs.                                                      |

| Jan 2001       | Delivery of power supply prototypes.                                                 |

|                | Test of characteristics.                                                             |

| Feb 2001       | Cables and power supply installation.                                                |

|                | First test of system with 1-2 detectors.                                             |

| March-May 2001 | Full test of system with N detectors.                                                |

|                | Test of different cable configurations.                                              |

| June 2001      | Commissioning of small scale version of system to power three groups of N detectors. |

| Jan 2002       | Delivery of small scale version of power supply system.                              |

| Feb - May 2002 | Test of whole system with three groups.                                              |

| July 2002      | Final cable selection and definition of the complete power supply system.            |

|                | Start cable and power supply system tendering.                                       |

|                |                                                                                      |

...

### **Development status**

• Power supplies

Unipolar baseline scheme adopted (0, +1.25V, +2.5V)

LV and HV supplies to float

PS modules power groups of ~60APV => ~ 1800 PS units

Cost model vs current to be provided

### • Cables 3 major sections

USC55 - detector racks ~100m Detector racks - patch panel ~40m Patch panel - module groups 4-5m preliminary costings exist, more detailed quotes to be obtained

### • Open questions

detailed module grouping

cost and time implications of any problems

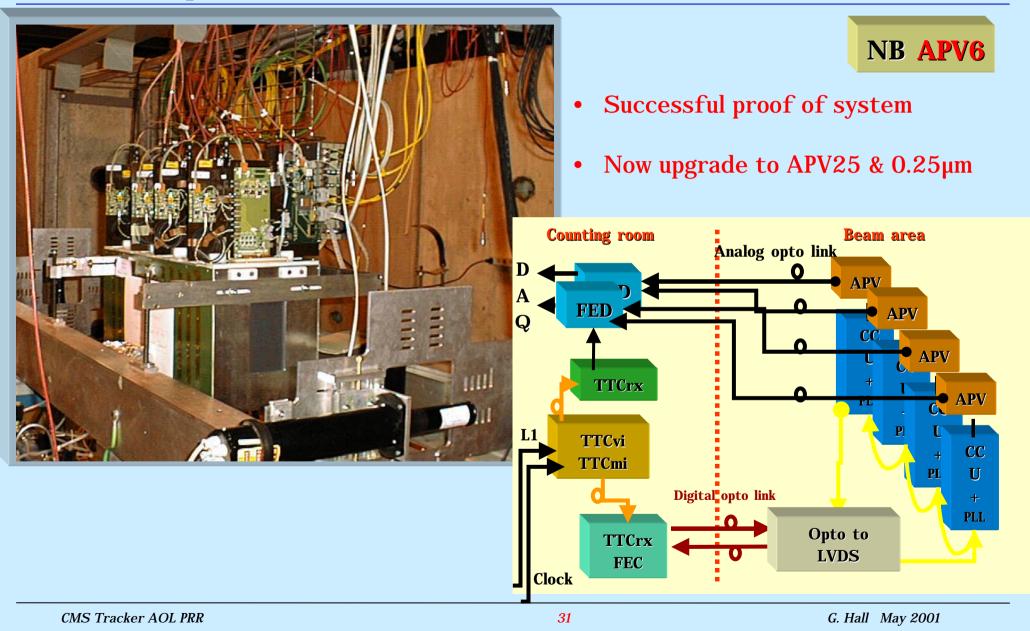

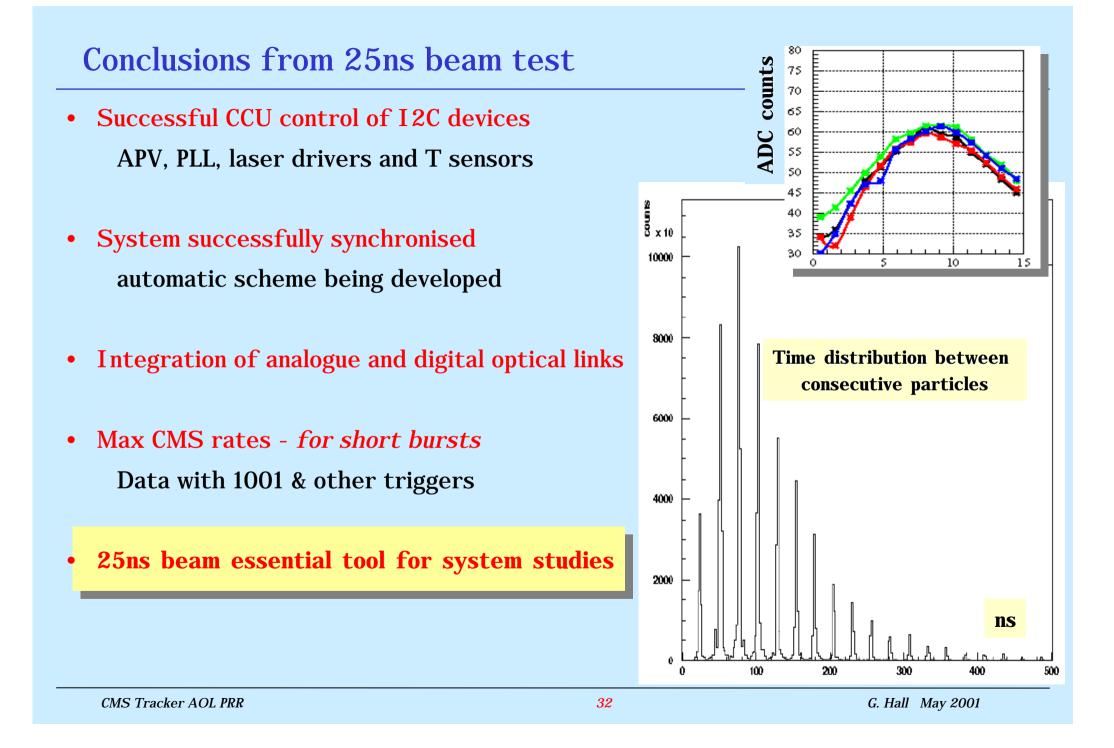

# LHC-like beam test

## May 2000

### Motivation

**Operate in an LHC like environment a tracker electronics chain:**

- FE read-out

- Control system

- Data Acquisition:

- Optical Links

APV chips FEC + CCUs + PLLs FEDs digital for timing and control analogue for data transfer

Debug the system and start answering questions such as:

- How to synchronise a modest number of detectors?

- Effect from close triggers on the data quality ?

- How long system can run continuously in an LHC like environment?

- + many others...

### X5 setup

## **Preparations for 2001 system test**

• Stages

•

System software and hardware well advanced Final hybrid assembly and operation working hybrid operational Module assembly and operation Multi-module installation **Operation of TOB rod** subsequently TEC & TIB units + several internal reviews ASIC final review FE hybrid Power & grounding DAQ & Control system

Aim to complete system test and hold ESR in December 2001

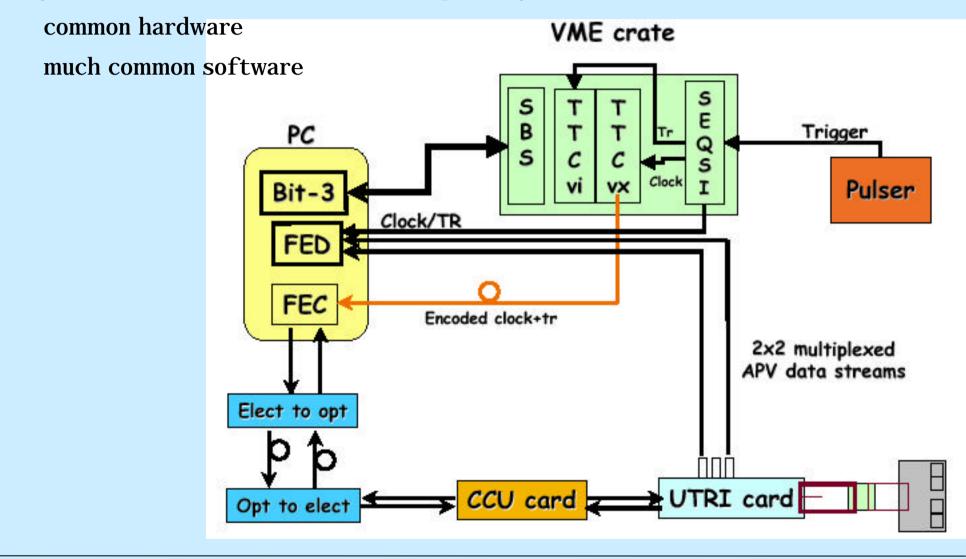

# PC based test-bench at CERN

• Symbiosis between module test set-up and system test

## Summary

- All component developments virtually complete

Performance, power, size, *cost* well understood

Radiation performance & robustness proven

FE ASIC testing systems & radiation qualification equipment in place

- Power supplies and cabling now under way

- System test advancing steadily schedule aggressive but no major obstacles foreseen

- Remaining risks

- costs need to complete optical tender to manage

- technical associated with component assembly and QA

- Production large scale orders: begin after December 2001 (& ESR) Milestone 200 & rod test provides final verification